Hybrid Bonding Market Size and Scope 2026 to 2035

What is Hybrid Bonding Market Size?

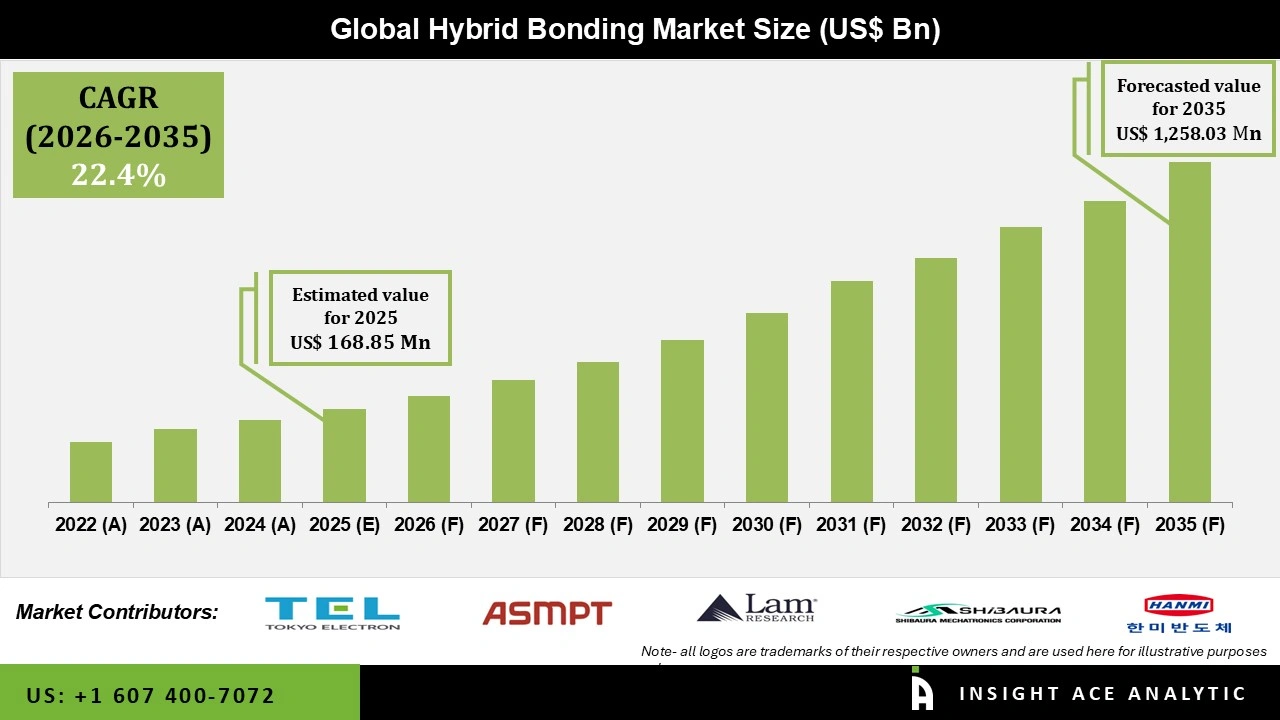

Global Hybrid Bonding Market Size is valued at USD 168.85 Mn in 2025 and is predicted to reach USD 1,258.03 Mn by the year 2035 at a 22.4% CAGR during the forecast period for 2026 to 2035.

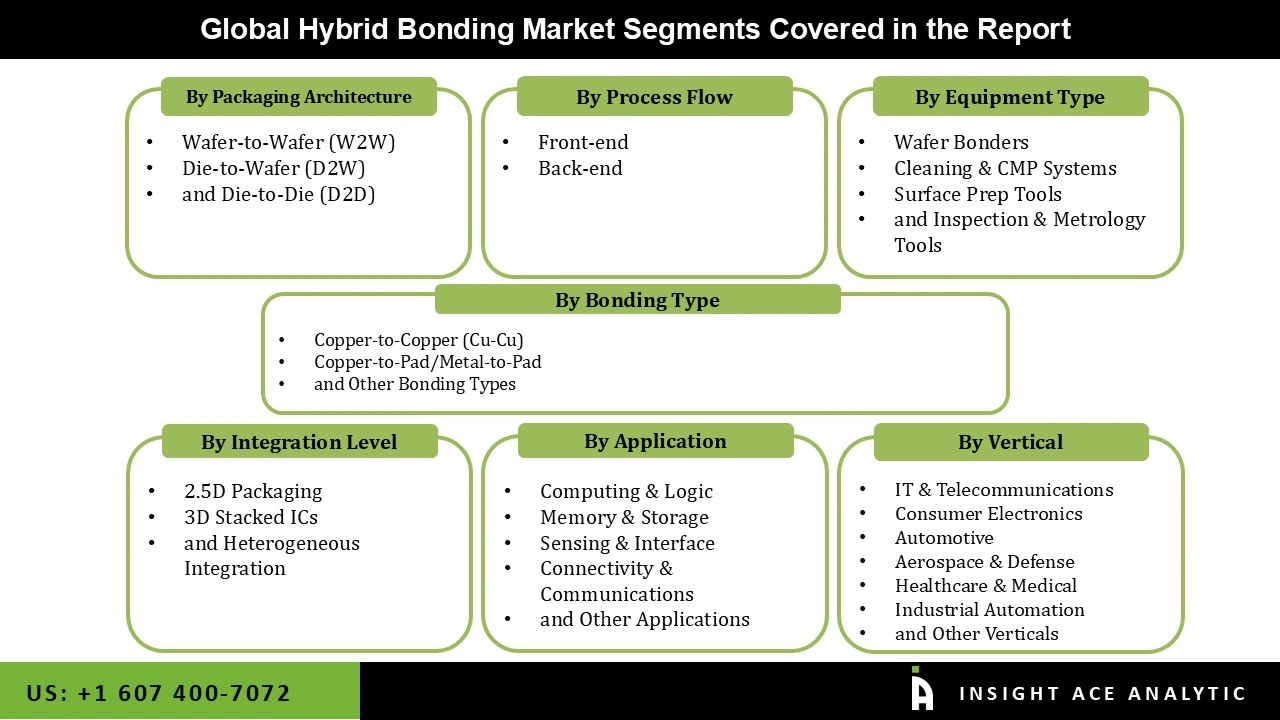

Hybrid Bonding Market Size, Share & Trends Analysis Distribution by Equipment Type (Wafer Bonders, Surface Prep Tools, Inspection & Metrology Tools, and Cleaning & CMP Systems), Bonding Type (Copper-to-Copper (Cu-Cu), Copper-to-Pad/Metal-to-Pad, and Others), Integration Level (2.5D Packaging, 3D Stacked Ics, and Heterogeneous Integration), Process Flow (Front-end and Back-end), Application (Memory & Storage, Computing & Logic, Connectivity & Communications, Sensing & Interface, and Others), Packaging Architecture (Wafer-to-Wafer (W2W), Die-to-Die (D2D), and Die-to-Wafer (D2W)), End-user (Consumer Electronics, IT & Telecommunications, Automotive, Industrial Automation, Healthcare & Medical, Aerospace & Defense, and Others), and Segment Forecasts, 2026 to 2035

Hybrid Bonding Market Key Takeaways:

|

Hybrid bonding is an advanced wafer-to-wafer or die-to-wafer interconnection technology that creates permanent, direct copper-to-copper bonds between stacked semiconductor components without solder bumps. This technique achieves ultra-fine-pitch interconnects, typically below 10 micrometres, while offering superior electrical performance, reduced power consumption, and improved thermal management compared to conventional packaging methods. By enabling denser, faster, and more reliable 3D integration, hybrid bonding has become a critical enabler for high-bandwidth memory, AI accelerators, and advanced system-on-chip designs where traditional packaging approaches cannot meet performance requirements.

The hybrid bonding market growth is being driven by several key drivers. The need for innovative packaging solutions is driven by the demand for high-performance computing, fueled by the development of 5G networks and the rise of artificial intelligence (AI). Furthermore, the implementation of 3D stacking, a crucial hybrid bonding application, enables notable improvements in chip performance and power efficiency. There is a significant market need for this functionality, which is especially crucial for mobile devices, high-performance servers, and cars. Additionally, the hybrid bonding market is expanding at an accelerated rate due to the increasing use of advanced bonding technology in packaging applications such as 3D packaging and semiconductor wafer-level packaging, which allows for the precise and accurate bonding of numerous materials.

In addition, the future growth of the hybrid bonding market is being shaped by significant technological developments. Higher bonding yields, enhanced dependability, and increased throughput are made possible by advancements in bonding materials, process methods, and equipment. The adaptability and usefulness of this technology are being further enhanced by the development of innovative hybrid bonding methods that combine various bonding techniques, such as adhesive bonding and thermo-compression bonding. Even though certain barriers, such as the high upfront costs of sophisticated machinery and intricate procedures, may prevent broader adoption, the long-term advantages of enhanced performance and reduced size are anticipated to surpass these drawbacks, further guaranteeing the hybrid bonding market growth.

Competitive Landscape

Which are the Leading Players in Hybrid Bonding Market?

- Applied Materials, Inc.

- EV Group (EVG)

- Tokyo Electron (TEL)

- ASMPT

- SUSS MicroTec SE

- Besi

- Kulicke & Soffa Industries, Inc.

- TORAY ENGINEERING Co., Ltd.

- KLA Corporation

- Lam Research Corporation

- SHIBAURA MECHATRONICS CORPORATION

- DISCO Corporation

- BEIJING U-PRECISION TECH CO., LTD

- Hanmi Semiconductor

- Onto Innovation

Market Dynamics

Driver

Rapid Growth in Heterogeneous Integration and Advanced Packaging

The increasing use of sophisticated packaging techniques and heterogeneous integration in semiconductor production is a major driver of the hybrid bonding market. The company is getting closer to three-dimensional chip stacking and system-in-package (SIP) solutions to incorporate various functions into a single package, enhancing overall performance while lowering shape element and power consumption. Wafer-to-wafer (W2W), chip-to-wafer (C2W), and chip-to-chip (C2C) bonding are made possible by hybrid bonding, which takes into account the smooth integration of various semiconductor materials and topologies. This is especially useful for packages that include AI accelerators, memory-storage devices, and high-bandwidth, standard-feel chips. Furthermore, government initiatives and funding for semiconductor research are hastening the introduction of hybrid bonding as a crucial facilitator of electronics of the future.

Restrain/Challenge

High Initial Implementation Costs

One of the main obstacles to the market growth of hybrid bonding technology is the high initial implementation costs. The cutting-edge die-to-wafer (D2W) bonders, sophisticated cluster clean benches, and specialized chemical mechanical planarization (CMP) tools are just a few examples of the ultra-high precision equipment needed for hybrid bonding, which differs from traditional packaging techniques in that placement accuracy must be less than $1 mu. It takes a significant amount of cash, frequently hundreds of millions of dollars, to set up a high-volume manufacturing (HVM) line that can meet such demanding front-end requirements. This expenditure is essential to control the intricacy and preserve the immaculate, flawless surfaces needed for a successful bond. As a result, the technology is mainly restricted to industry leaders due to the high barrier to entry, which restricts the hybrid bonding market expansion.

Heterogeneous Integration Segment is Growing at the Highest Rate in the Hybrid Bonding Market

In 2025, the Heterogeneous Integration category dominated the Hybrid Bonding market as the industry quickly switched to chiplet-based architectures, which combine accelerators, logic, memory, analog, and radio frequency into one device. The ultra-dense vertical interconnects needed to provide these multi-die assemblies with high bandwidth, low power consumption, and enhanced system-level performance are made possible via hybrid bonding. Additionally, the need for heterogeneous integration is being further increased by the growing reliance on chiplet architectures in AI accelerators, HPC processors, and sophisticated mobile SoCs. In addition, the hybrid bonding adoption is fueled by the high cost and performance benefits that come from combining various process nodes, materials, and functional blocks. The most active growth segment is heterogeneous integration as system-level scalability becomes crucial.

Wafer-to-Wafer (W2W) Segment is Expected to Drive the Hybrid Bonding Market

The Wafer-to-Wafer (W2W) category held the largest share in the Hybrid Bonding market in 2025. Since wafer-to-wafer hybrid bonding allows for full-surface metal-oxide interconnects, which essentially remove the parasitic resistance and capacitance associated with silicon vias, it is becoming a crucial production step. Manufacturers can co-integrate logic, memory, photonic, and sensor layers into a single monolithic three-dimensional device by stacking fully processed wafers with nanometer-level alignment accuracy, providing enormous bandwidth and reduced energy per bit. Wafer-to-wafer designs are now essential for high-performance computing, mobile CPUs, and AI accelerators due to these quantifiable system benefits, which have encouraged foundries and OSATs to increase their capacity. Additionally, equipment vendors are profiting from the booking of orders for cluster systems, bonding aligners, and plasma activation tools. The ensuing cycle of investment, demand, and ecosystem development drives the current global hybrid bonding technology market's steady, strong expansion.

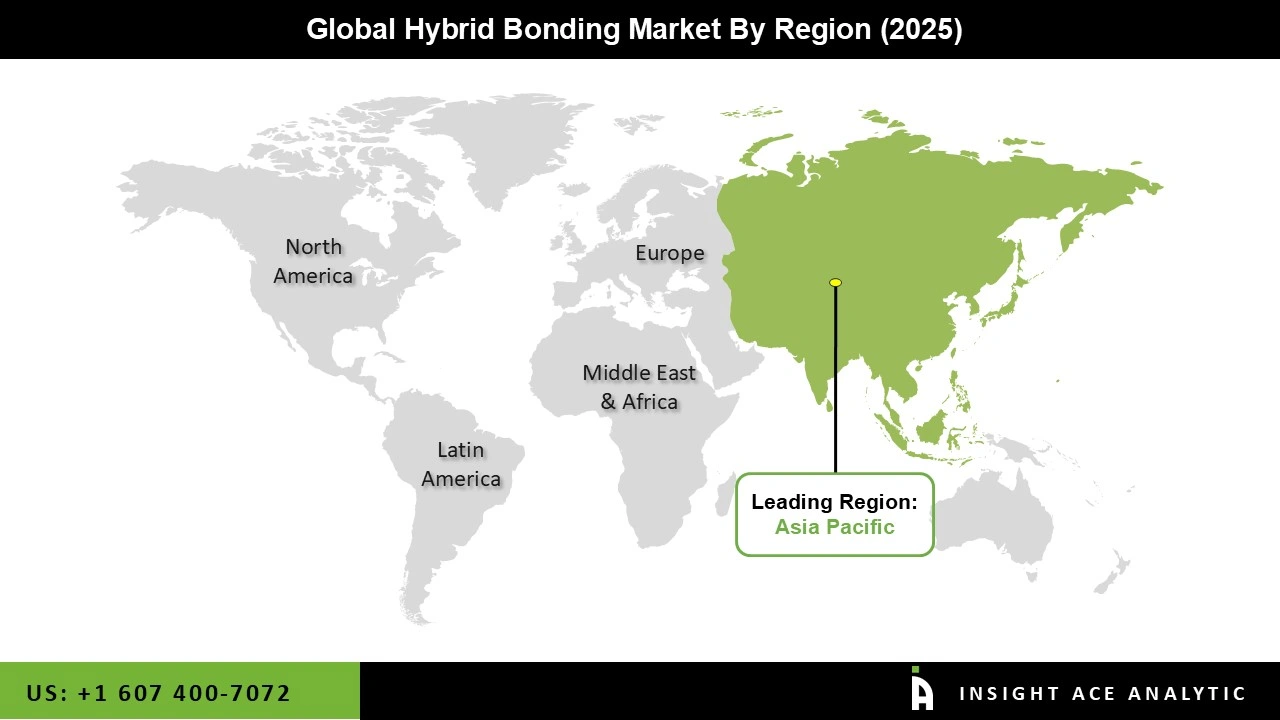

Why Asia Pacific Led the Hybrid Bonding Market?

The Hybrid Bonding market was dominated by the Asia Pacific region in 2025 due to its strong concentration of major semiconductor manufacturers, cutting-edge R&D centers, and government support for chip development. For next-generation semiconductor packaging, businesses are heavily investing in hybrid bonding, particularly in the fields of artificial intelligence (AI), high-performance computing (HPC), and information centers.

Additionally, with the growing need for AI accelerators, 5G infrastructure, and small, high-efficiency chips driving market growth, the US is becoming a center for hybrid bonding innovation and widespread implementation. The demand for sophisticated medical equipment is fueled by the growing investment in the healthcare industry, which in turn propels market expansion.

Key Development

May 2025: The XBC300 Gen2 D2W platform, a tailored bonding solution that completes SUSS MicroTec SE's hybrid bonding range, was unveiled. With this new platform, it further solidifies its position as a leader in providing fully integrated die-to-wafer (D2W) hybrid bonding solutions that are suited to the demands of modern manufacturing. With its support for D2W bonding on 200mm and 300mm substrates, the system can precisely meet extremely strict inter-die spacing requirements.

Hybrid Bonding Market Report Scope :

| Report Attribute | Specifications |

| Market size value in 2025 | USD 168.85 Mn |

| Revenue forecast in 2035 | USD 1,258.03 Mn |

| Growth Rate CAGR | CAGR of 22.4% from 2026 to 2035 |

| Quantitative Units | Representation of revenue in US$ Bn and CAGR from 2026 to 2035 |

| Historic Year | 2022 to 2025 |

| Forecast Year | 2026-2035 |

| Report Coverage | The forecast of revenue, the position of the company, the competitive market structure, growth prospects, and trends |

| Segments Covered | Equipment Type, Bonding Type, Integration Level, Process Flow, Application, Packaging Architecture, End-user, and By Region |

| Regional Scope | North America; Europe; Asia Pacific; Latin America; Middle East & Africa |

| Country Scope | U.S.; Canada; U.K.; Germany; China; India; Japan; Brazil; Mexico; The UK; France; Italy; Spain; China; Japan; India; South Korea; Southeast Asia; South Korea; Southeast Asia |

| Competitive Landscape | Applied Materials, Inc., EV Group (EVG), Tokyo Electron (TEL), ASMPT, SUSS MicroTec SE, Besi, Kulicke & Soffa Industries, Inc., TORAY ENGINEERING Co., Ltd., KLA Corporation, Lam Research Corporation, SHIBAURA MECHATRONICS CORPORATION, DISCO Corporation, BEIJING U-PRECISION TECH CO., LTD, Hanmi Semiconductor, and Onto Innovation |

| Customization Scope | Free customization report with the procurement of the report, Modifications to the regional and segment scope. Geographic competitive landscape. |

| Pricing and Available Payment Methods | Explore pricing alternatives that are customized to your particular study requirements. |

Segmentation of Hybrid Bonding Market :

Hybrid Bonding Market by Equipment Type-

- Wafer Bonders

- Surface Prep Tools

- Inspection & Metrology Tools

- Cleaning & CMP Systems

Hybrid Bonding Market by Bonding Type-

- Copper-to-Copper (Cu-Cu)

- Copper-to-Pad/Metal-to-Pad

- Others

Hybrid Bonding Market by Integration Level-

- 2.5D Packaging

- 3D Stacked ICs

- Heterogeneous Integration

Hybrid Bonding Market by Process Flow-

- Front-end

- Back-end

Hybrid Bonding Market by Application-

- Memory & Storage

- Computing & Logic

- Connectivity & Communications

- Sensing & Interface

- Others

Hybrid Bonding Market by Packaging Architecture-

- Wafer-to-Wafer (W2W)

- Die-to-Die (D2D)

- Die-to-Wafer (D2W)

Hybrid Bonding Market by End-user-

- Consumer Electronics

- IT & Telecommunications

- Automotive

- Industrial Automation

- Healthcare & Medical

- Aerospace & Defense

- Others

Hybrid Bonding Market By Region-

- North America-

- The US

- Canada

- Europe-

- Germany

- The UK

- France

- Italy

- Spain

- Rest of Europe

- Asia-Pacific-

- China

- Japan

- India

- South Korea

- South East Asia

- Rest of Asia Pacific

- Latin America-

- Brazil

- Argentina

- Mexico

- Rest of Latin America

- Middle East & Africa-

- GCC Countries

- South Africa

- Rest of Middle East and Africa

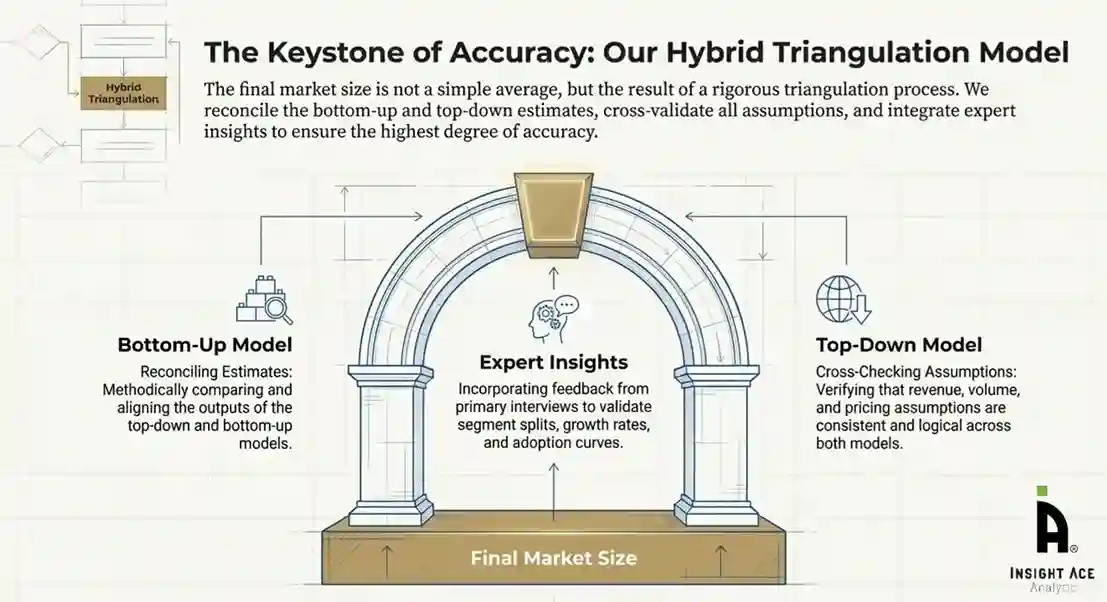

Research Design and Approach

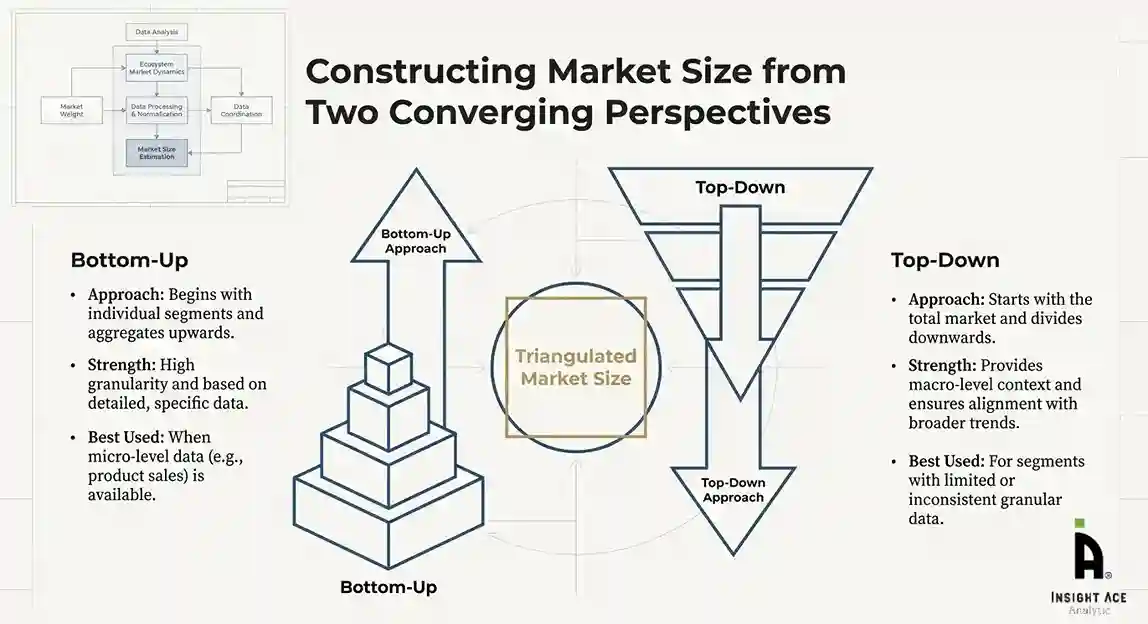

This study employed a multi-step, mixed-method research approach that integrates:

- Secondary research

- Primary research

- Data triangulation

- Hybrid top-down and bottom-up modelling

- Forecasting and scenario analysis

This approach ensures a balanced and validated understanding of both macro- and micro-level market factors influencing the market.

Secondary Research

Secondary research for this study involved the collection, review, and analysis of publicly available and paid data sources to build the initial fact base, understand historical market behaviour, identify data gaps, and refine the hypotheses for primary research.

Sources Consulted

Secondary data for the market study was gathered from multiple credible sources, including:

- Government databases, regulatory bodies, and public institutions

- International organizations (WHO, OECD, IMF, World Bank, etc.)

- Commercial and paid databases

- Industry associations, trade publications, and technical journals

- Company annual reports, investor presentations, press releases, and SEC filings

- Academic research papers, patents, and scientific literature

- Previous market research publications and syndicated reports

These sources were used to compile historical data, market volumes/prices, industry trends, technological developments, and competitive insights.

Primary Research

Primary research was conducted to validate secondary data, understand real-time market dynamics, capture price points and adoption trends, and verify the assumptions used in the market modelling.

Stakeholders Interviewed

Primary interviews for this study involved:

- Manufacturers and suppliers in the market value chain

- Distributors, channel partners, and integrators

- End-users / customers (e.g., hospitals, labs, enterprises, consumers, etc., depending on the market)

- Industry experts, technology specialists, consultants, and regulatory professionals

- Senior executives (CEOs, CTOs, VPs, Directors) and product managers

Interview Process

Interviews were conducted via:

- Structured and semi-structured questionnaires

- Telephonic and video interactions

- Email correspondences

- Expert consultation sessions

Primary insights were incorporated into demand modelling, pricing analysis, technology evaluation, and market share estimation.

Data Processing, Normalization, and Validation

All collected data were processed and normalized to ensure consistency and comparability across regions and time frames.

The data validation process included:

- Standardization of units (currency conversions, volume units, inflation adjustments)

- Cross-verification of data points across multiple secondary sources

- Normalization of inconsistent datasets

- Identification and resolution of data gaps

- Outlier detection and removal through algorithmic and manual checks

- Plausibility and coherence checks across segments and geographies

This ensured that the dataset used for modelling was clean, robust, and reliable.

Market Size Estimation and Data Triangulation

Bottom-Up Approach

The bottom-up approach involved aggregating segment-level data, such as:

- Company revenues

- Product-level sales

- Installed base/usage volumes

- Adoption and penetration rates

- Pricing analysis

This method was primarily used when detailed micro-level market data were available.

Top-Down Approach

The top-down approach used macro-level indicators:

- Parent market benchmarks

- Global/regional industry trends

- Economic indicators (GDP, demographics, spending patterns)

- Penetration and usage ratios

This approach was used for segments where granular data were limited or inconsistent.

Hybrid Triangulation Approach

To ensure accuracy, a triangulated hybrid model was used. This included:

- Reconciling top-down and bottom-up estimates

- Cross-checking revenues, volumes, and pricing assumptions

- Incorporating expert insights to validate segment splits and adoption rates

This multi-angle validation yielded the final market size.

Forecasting Framework and Scenario Modelling

Market forecasts were developed using a combination of time-series modelling, adoption curve analysis, and driver-based forecasting tools.

Forecasting Methods

- Time-series modelling

- S-curve and diffusion models (for emerging technologies)

- Driver-based forecasting (GDP, disposable income, adoption rates, regulatory changes)

- Price elasticity models

- Market maturity and lifecycle-based projections

Scenario Analysis

Given inherent uncertainties, three scenarios were constructed:

- Base-Case Scenario: Expected trajectory under current conditions

- Optimistic Scenario: High adoption, favourable regulation, strong economic tailwinds

- Conservative Scenario: Slow adoption, regulatory delays, economic constraints

Sensitivity testing was conducted on key variables, including pricing, demand elasticity, and regional adoption.

Request Customization

Add countries, segments, company profiles, or extend forecast — free 10% customization with purchase.

Customize This Report →Enquire Before Buying

Speak with our analyst team about scope, methodology, pricing, or deliverable formats.

Enquire Now →Frequently Asked Questions

Hybrid Bonding Market Size is valued at USD 168.85 Mn in 2025 and is predicted to reach USD 1,258.03 Mn by the year 2035

Hybrid Bonding Market is expected to grow at a 22.4% CAGR during the forecast period for 2026 to 2035

Applied Materials, Inc., EV Group (EVG), Tokyo Electron (TEL), ASMPT, SUSS MicroTec SE, Besi, Kulicke & Soffa Industries, Inc., TORAY ENGINEERING Co., Ltd., KLA Corporation, Lam Research Corporation, SHIBAURA MECHATRONICS CORPORATION, DISCO Corporation, BEIJING U-PRECISION TECH CO., LTD, Hanmi Semiconductor, Onto Innovation and Other.

Hybrid Bonding Market is segmented into Equipment Type, Bonding Type, Integration Level, Process Flow, Application, Packaging Architecture, End-user, and Other.

Asia Pacific Region is leading the Hybrid Bonding Market.